In this section a short recap is given on the most important design steps and conclusions on the antenna amplifier

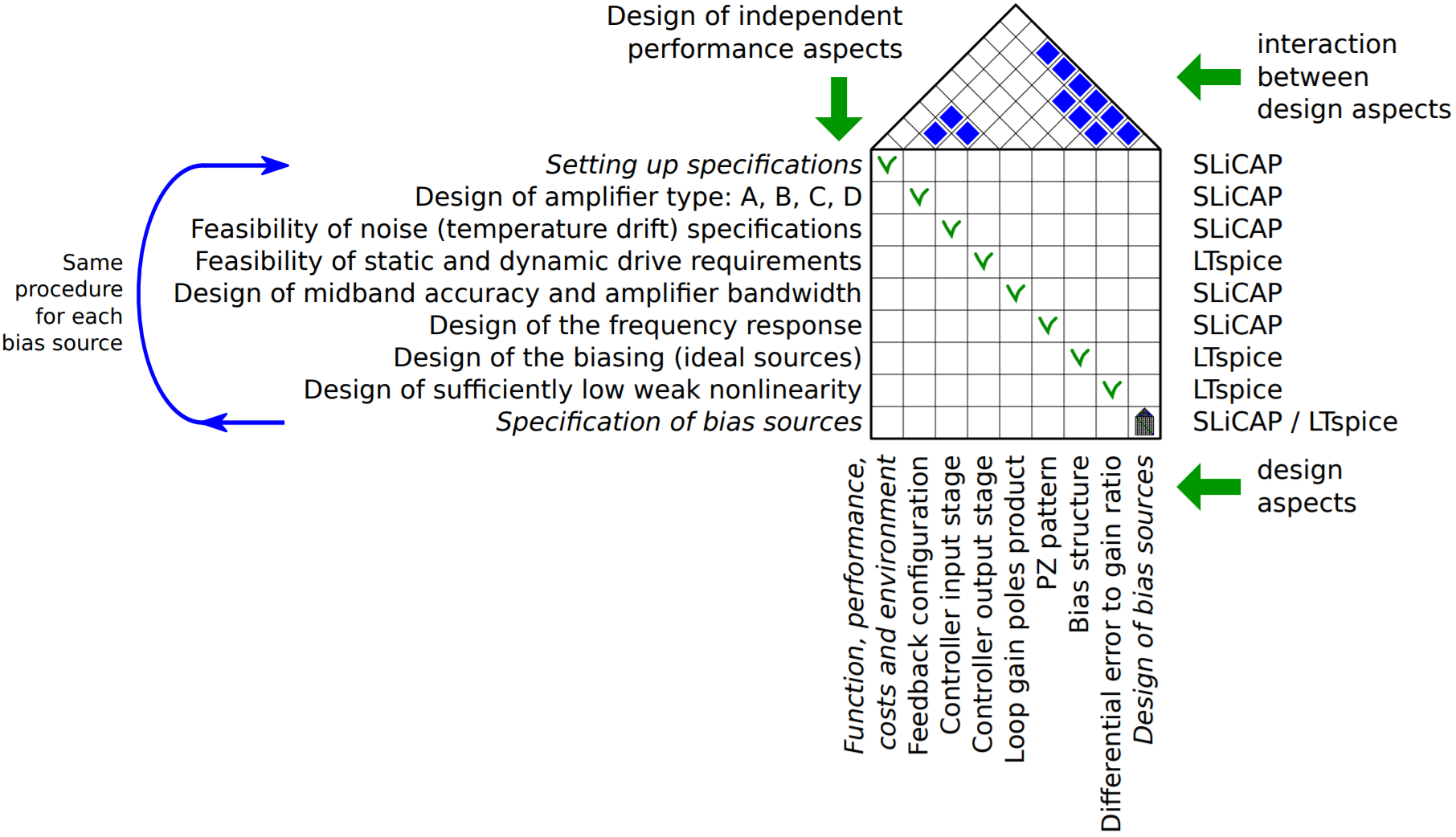

The design of the amplifier that was implemented using CMOS180 technology was done using a structured design approach outlined using the design pyramid shown below.

During the design both LTspice and SLiCAP are used, SLiCAP comes with a great number of benefits compared to LTspice that will help with the design process by providing design methods that are easy to handle compared to LTspice. One of the most important design advantages is that the biasing of the circuit can be left till the end of the design process.

The design started first with a single CS stage, the most simple design available, from which driving capabilities and noise performance is determined. If the design could not even be reached by this design the specification are too stringent and we have our final design conclusion

First the feasibility of the riving capability was measured using LTspice, here we came to the conclusion that with using a 50$\Omega$ brute force resistor the driving specification could be met with the single CS stage. Therefore the width of the transistor was determined and other device characteristics were measured such as the transistor cutoff frequency and transconductance.

Before we can use SLiCAP in the following stage, which is the noise analysis, we need to know how well the SLiCAP transistor model compares to the LTspice model. Different figures were made such as the magnitude and phase of the transimpedance of the transistor and of the impedance. Comparing the simulations gave the conclusion that the SLiCAP model was modelled sufficiently accurate for the design of the amplifier, only at very high and very low frequencies (outside the frequency range of interest) a deviation from the two models was visible.

Next is determining the feasibility of the noise specification, herefore both the noise floor and the 1/f noise have been studied from which a showstopper value of the width of the transistor has been determined this being 7$\mu m$. In order to take the 1/f noise characteristic into account a design margin was set up that gives a figure on how much room is left until the noise specification has been met, as long as this value is larger than 1 the design is sufficient. Of course the goal is to have some more headroom in this stage of the design so that any additional noise added in later design steps wont decrease this margin below 1. From the initial calculation the design margin was found to be 12.8, which means that the current design still has much more room left to meet the noise specification.

The following stage of the design concerns itself with the dynamic and static drive requirements and is carried out in LTspice. Instead of a simple CS stage a AB output stage (parallel complementary connection) , which is a balanced stage, is investigated for its feasibility in the design. The balanced stage will provide yield a current noise spectrum twice that of a single CS stage and a voltage noise spectrum that is half of that. It also provides a better voltage swing compared to the CS stage and a lower quiescent current at zero input signal. From the simulations it was found that the parallel complementary stage was sufficient to act as the output stage of the amplifier since it was able to fulfil the driving requirements.

Next the input stage of the amplifier which is responsible for the noise requirement is chosen to be a anti-series connection of 2 NMOS transistors, it provides that there is no offset present at the input of the amplifier. This combination together with the AB output stage provides a single signal inversion which will make negative feedback possible. However the downside of this input stage is that the device needs twice the area and current compared to the single CS stage in order to have the same noise performance.

Now that the controller configuration has been decided the feedback topology can be designed, since the input of the amplifier is capacitive and we desire ESD protection on the input a capacitive feedback topology was chosen. Implementing the simple implementation gives for the noise a even higher design margin compared to when only a single CS stage was used for the design.

The following stage is performing a frequency analysis of the amplifier design, the initial simulations gave a quite bad result as expected. Therefore it was decided that additional frequency compensation was needed. The initial simulation gave too much peaking and a very wide bandwidth $>1GHz$, compared to the desired MFM magnitude characteristics and a $30MHz$ bandwidth. First a phantom zero was inserted in the feedback loop by placing a resistor in parallel with the output capacitance of the antenna. From which a value of $R_{PHZ} = 13.86 \Omega$ was determined which gave the desired MFM characteristics.

Additionally bandwidth reduction could be implemented to aid in the design of the amplfier since the available bandwidth is larger than needed, in the end a additional phantom zero was placed at the output of the amplifier by placing a inductor of $0.4\mu H$ in series with the output resitor. This reduced the bandwidth to almost the specified bandwidth of $30MHz$ while not introducing any additional peaking at higher frequencies, this reduction of bandwidth benefits the loopgain since now more loopgain is available at lower frequencies. However implementing such a rather big inductor on a chip might prove to be difficult in a real application.

Now that the entire design has been validated in SLiCAP the biasing network can be designed in LTspice and the result of both circuits can be compared.

First a very simple biasing network consisting of ideal and floating sources is made to validate the design, and the LTspice simulation results showed very close accuracy to the SLiCAP simulation results. Afterwards the floating source was eliminated and the results still showed very close resemblance to each other, the only change that was visible is that the LTspice simulation now showed a little bit more intermodulation distortion. The final biasing circuit in which the ideal current sources are all replaced by voltage references showed a too high noise floor which did not meet the specification unfortunately.

As a final suggestion to the design as shown in the pyramid above, now that we are at the final step of the design we can jump back using all the already obtained SLiCAP files to repeat the procedure again to obtain a design which does meet the noise limitation using the final biasing network.